以“四个面向”为引领,复旦大学微电子学院教授周鹏团队针对主流电荷存储器技术,发现了制约硅基闪存技术的原理瓶颈,提供了可以应用于硅材料的器件模型,实现了匹敌易失内存技术的超快速度,为统一存储器的发展提供了技术途径。北京时间6月3日,相关成果以《基于范德瓦尔斯异质结构的超快非易失闪存》(“Ultrafast non-volatile flash memory based on van der Waals heterostructures”)为题在《自然-纳米技术》(Nature Nanotechnology)在线发表。

闪存自1967年发明以来,由于其高密度低成本的特性,已经占据了先进非易失存储技术99%的市场。然而自从东芝公司实现商业化技术后,工作在量子隧穿机制下的硅基闪存编程时间一直在百微秒量级,无法实现对速度有较高要求的内存级应用。那么量子隧穿机制是注定不能实现更快的速度吗?

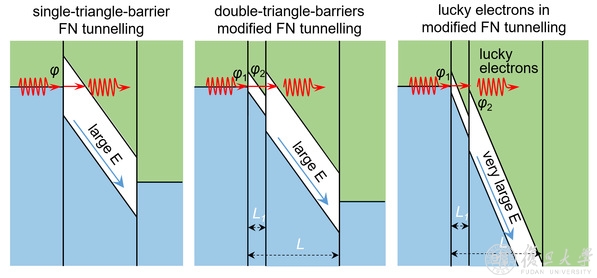

周鹏团队从源头出发,首次发现了双三角隧穿势垒超快电荷存储机理,突破了传统经验束缚,获得了内存DRAM技术级编程速度。研究发现,在存储与擦除的工作过程中,势垒高度决定了电荷隧穿通过的难易程度,栅耦合比决定了栅极控制电压产生的电荷密度,良好界面保证了不会引入额外沾污或缺陷。从以上三大方面看,现有的硅/氧化硅界面非常完美,周鹏团队发现并证明了栅耦合比、势垒高度是决定电荷存储器速度的根本因素。

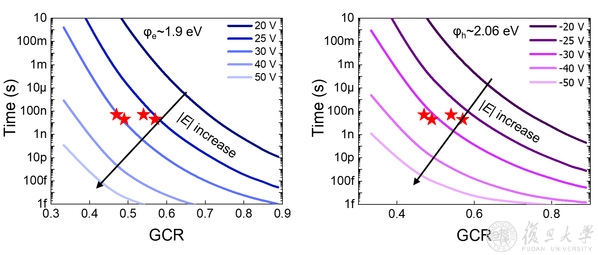

周鹏团队根据此超快电荷存储原理建立了通用器件模型,设计并制备出同时具备三大要素的范德华异质结闪存,采用工业界标准阈值漂移测试和高温加速老化测试方案,验证了20纳秒编程时间和10年数据保持能力;并对器件进行了理论模拟计算,实验数据和理论模拟结果吻合一致;同时探讨了三大要素的不同程度缺失导致器件速度衰退的物理机制,为在硅体系中开展应用指出了原则性的研发路径。

图1.双三角隧穿势垒超快电荷存储机理示意图

图2.存储器中电子与空穴编程速度与栅耦合比、电场的定量关系图

微电子学院博士生刘岚和博士后刘春森为论文第一作者,微电子学院教授陈时友和周鹏为论文通讯作者。研究工作得到了国家自然科学基金杰出青年科学基金、应急重点项目及上海市集成电路重点专项等项目的资助,以及教育部创新平台和专用集成电路与系统国家重点实验室的支持。

① 凡本站注明“稿件来源:教育在线”的所有文字、图片和音视频稿件,版权均属本网所有,任何媒体、网站或个人未经本网协议授权不得转载、链接、转贴或以其他方式复制发表。已经本站协议授权的媒体、网站,在下载使用时必须注明“稿件来源:教育在线”,违者本站将依法追究责任。

② 本站注明稿件来源为其他媒体的文/图等稿件均为转载稿,本站转载出于非商业性的教育和科研之目的,并不意味着赞同其观点或证实其内容的真实性。如转载稿涉及版权等问题,请作者在两周内速来电或来函联系。

教育在线

教育在线